# A 60 GHz 4-bit Phase Shifter Using 0.13 µm RFCMOS Technology

이성권,김지훈,이종욱

Kyung Hee University, Suwon 446-701, Korea, jwee@khu.ac.kr

## I. Introduction

For millimeter-wave (60 GHz) phase array system, a 4-bit phase shifter was fabricated using Dongbu Hitek 0.13 um RFCMOS technology. The phase shifter were designed by combining loaded-line structure for 22.5 and 45 degree phase shifting, and switched-line structure for 90 and 180 degree phase shift. Simulation result of the 4-bit phase shifter showed an insertion loss of about  $10\pm0.5$  dB at 60 GHz. Chip size of the 4-bit phase shifter was  $1.2 \times 0.7 \text{ mm}^2$ . Initial evaluation of the switched-line phase shifter (90 and 180 degree phase shift) showed an insertion loss of 6.7 dB at 60 GHz.

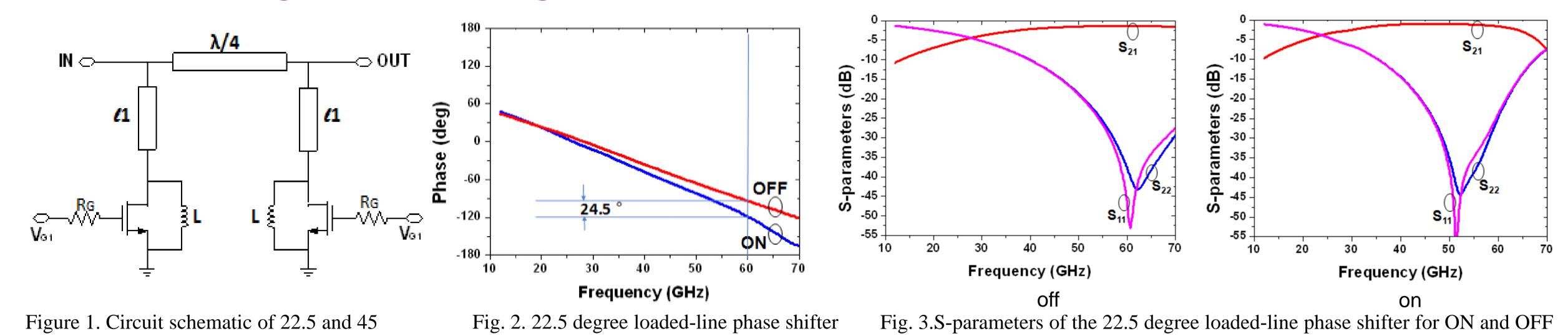

# II. 22.5 degree & 45 degree Loaded-Line Phase Shifter

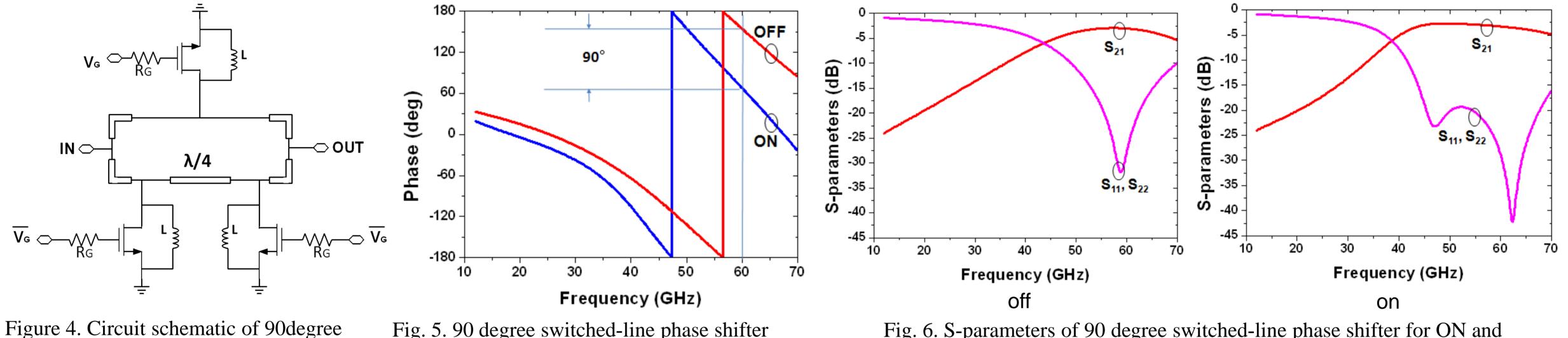

III. 90 degree & 180 degree Switched-Line Phase Shifter

characteristics for ON and OFF states.

states.

switched-line phase shifter.

degree loaded-line phase shifter.

Fig. 5. 90 degree switched-line phase shifter characteristics for ON and OFF states.

Fig. 6. S-parameters of 90 degree switched-line phase shifter for ON and OFF states.

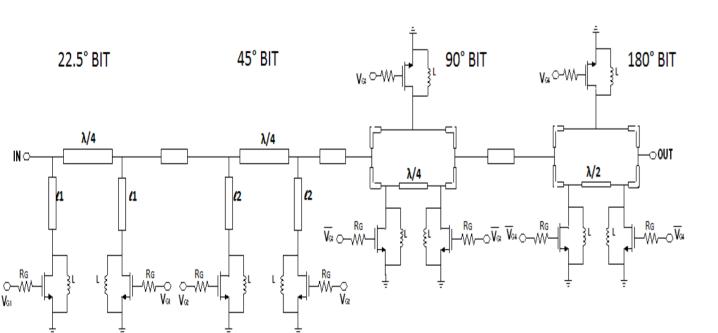

#### IV. 4-bit Phase Shifter

### V. Measured results (2-bit)

(a)

Figure 7. Circuit schematic of 4-bit phase shifter.

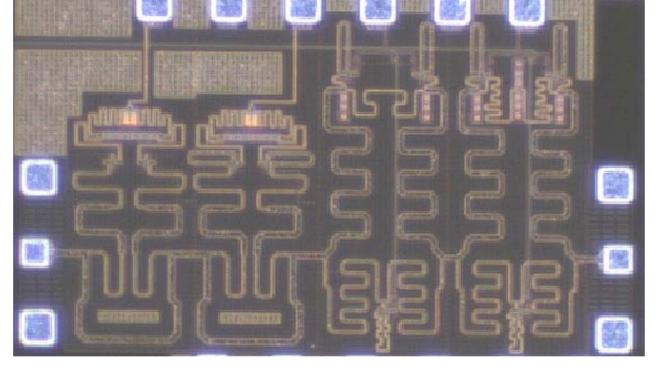

Fig. 8. Photograph of the 4-bit phase shifter fabricated using Dongbu Hitek 0.13um RFCMOS process. Size is  $1230 \times 730 \text{ um}^2$ .

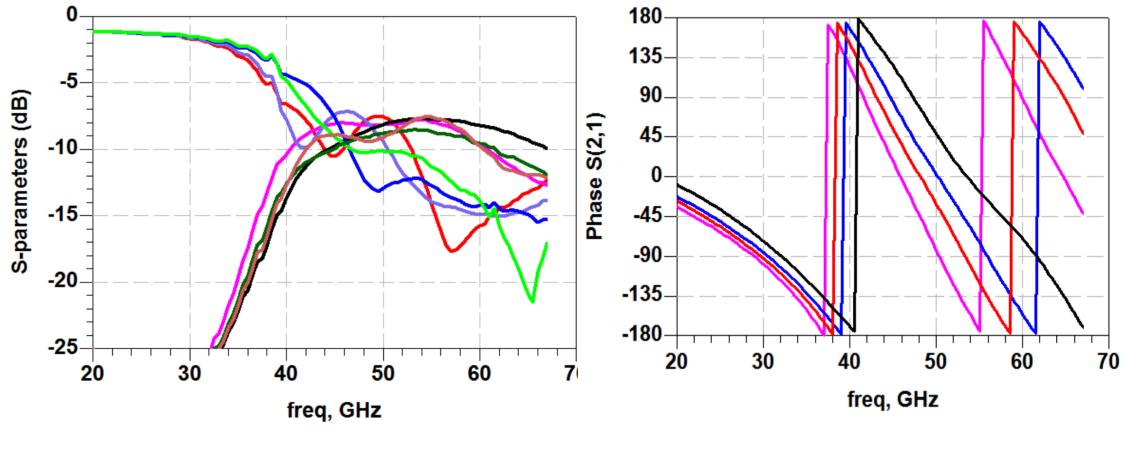

Fig. 9. Measured results of the 2-bit (90 and 180 degree) phase shifter, (a) insertion loss, (b) phase shifting characteristics.

(b)

### **VI. Conclusions**

Initial phase shifter for 60 GHz phase array application was successfully designed and fabricated using Dongbu Hitek 0.13um RFCMOS process. The measured data measured on-wafer up to 67 GHz using Agilent E8361A PNA shows promising results. In the future, the following revision will be done: 1) including the effect of measurement pad, 2) correct less than design phase shifting values, 3) reducing the chip size, 4) phase re-design and achieving improved results using 90nm CMOS process.

### Acknowledgement

This work was supported by the Korea Science and Engineering Foundation (KOSEF) grant funded by the Korea government (MEST) (No. 2009-0078157). The authors acknowledge Dongbu HiTek for 0.13 µm CMOS chip fabrication. The CAD tools used in this work was supported by the IDEC.

#### References

[1] R. V. Garver, "Broad-band diode phase shifter" IEEE Trans. Microwave Theory Tech, vol. MTT-20, pp. 314-323, May 1972. [2] H. A. Atwater, "Circuit Design of the Loaded-Line Phase Shifter" IEEE Transactions on Microwave Theory and Tech., vol. MTT-33, no. 7, July. 1985.